- 您现在的位置:买卖IC网 > Sheet目录1203 > COREPCIF-RM (Microsemi SoC)IP MODULE COREPCIF

�� �

�

�

�Introduction�

�CorePCIF� v4.0�

�Core� Versions�

�This� handbook� applies� to� CorePCIF� v3.6.� The� release� notes� provided� with� the� core� list� known� discrepancies� between�

�this� handbook� and� the� core� release� associated� with� the� release� notes.�

�CorePCIF� Device� Requirements�

�CorePCIF� includes� Target� and/or� Master� functions.� The� core� also� has� an� option� for� a� built-in� DMA� controller.�

�There� are� eight� implementations� available� for� the� core.� The� SMALL32� implementation� is� the� smallest� Target� core�

�possible� but� does� not� support� zero-wait-state� transfers;� TARG32� does� support� zero-wait-state� transfers.� MAST32� is� the�

�smallest� Master-only� core� possible.� TARGDMA32� implements� a� typical� Target� and� Master� function.� TARGMAST32�

�implements� a� fully� configured� core.� The� remaining� four� implementations� are� 64-bit� versions� of� the� 32-bit�

�implementations.� Table� 1� describes� example� implementations.�

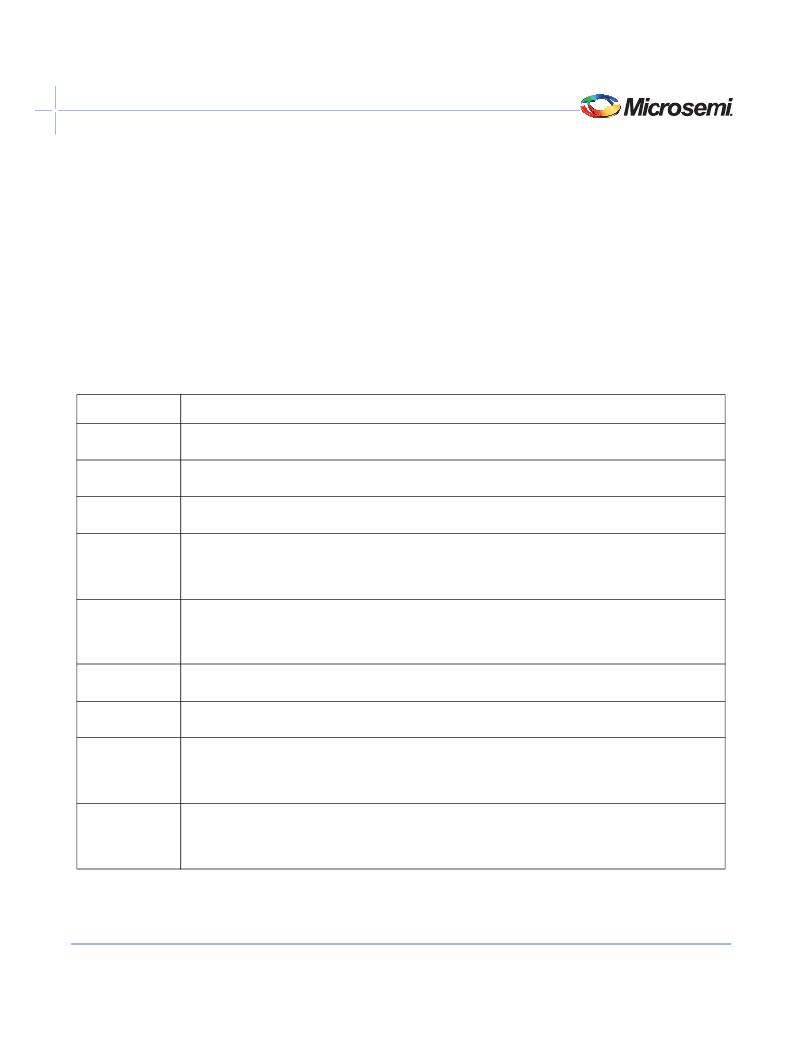

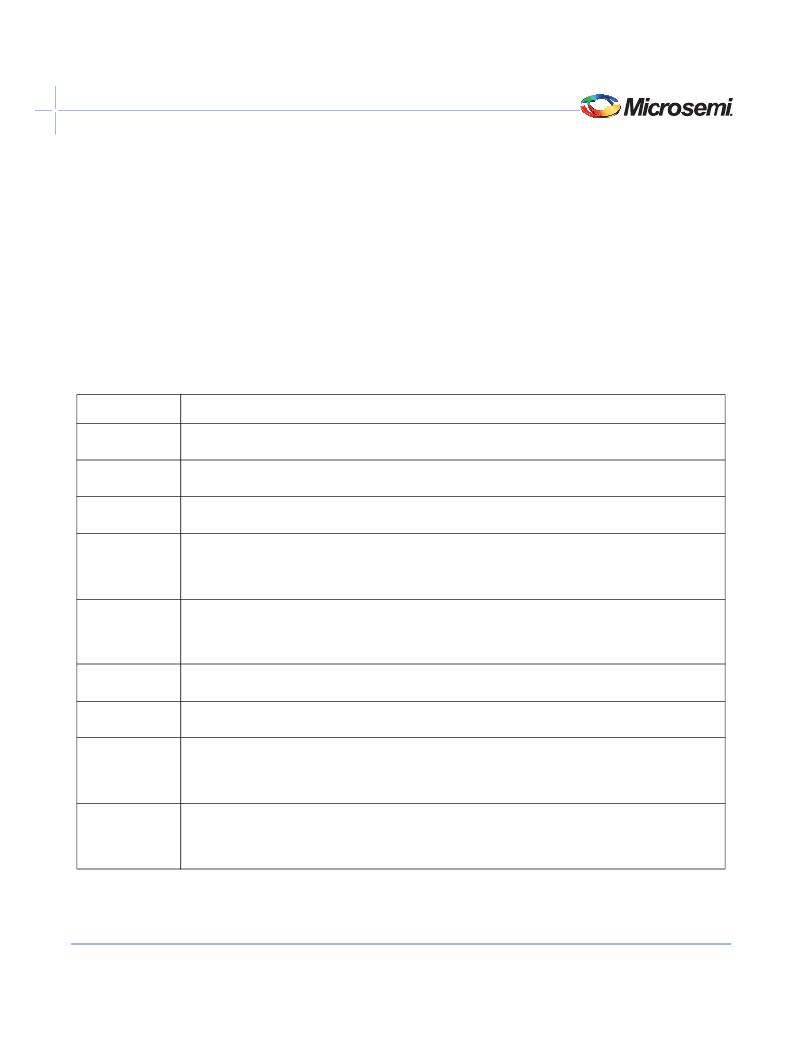

�Table� 1� ·� Example� Implementations�

�6�

�Implementation�

�SMALL32�

�TARG32�

�MAST32�

�TARGDMA32�

�TARGMAST32�

�TARG64�

�MAST64�

�TARGDMA64�

�TARGMAST64�

�Description�

�32-bit� Target-only� core� with� a� single� base� address� register� (BAR).� The� slow� read� function� is� enabled.� Interrupts,�

�BAR� overflow,� and� hot-swap� features� are� disabled.�

�32-bit� Target-only� core� with� a� single� 64� kB� BAR.� The� FIFO� recovery� logic� is� not� implemented.� BAR� overflow�

�logic� and� hot-swap� features� are� disabled.�

�32-bit� Master-only� core� with� a� single� 64� kB� BAR.� The� FIFO� recovery� logic� is� not� implemented.� Direct� DMA� is�

�enabled.�

�32-bit� Target� and� Master� function� with� a� single� 64� kB� BAR.� DMA� registers� are� accessible� from� the� PCI� side� and�

�are� memory-mapped� in� the� second� BAR.� The� FIFO� recovery� logic� is� not� implemented.� BAR� overflow� logic� and�

�hot-swap� features� are� disabled.� Backend� access� to� the� DMA� registers� is� not� implemented.� Direct� DMA� is�

�disabled.�

�32-bit� Target� and� Master� function� with� five� memory� BARs� that� have� variable� sizes� from� 64� kB� to� 1� GB.� The�

�DMA� registers� are� memory-mapped� to� the� sixth� BAR.� All� of� the� memory� BARs� include� the� FIFO� recovery�

�logic.� The� Expansion� ROM� address� registers� are� also� implemented.� BAR� overflow� logic� and� hot-swap� features�

�are� enabled.� Backend� access� to� the� DMA� registers� is� also� implemented.� Direct� DMA� is� enabled.�

�64-bit� Target-only� core� with� a� single� 64� kB� BAR.� The� FIFO� recovery� logic� is� not� implemented.� BAR� overflow�

�logic� and� hot-swap� features� are� disabled.� Direct� DMA� is� disabled.�

�64-bit� Master-only� core� with� a� single� 64� kB� BAR.� The� FIFO� recovery� logic� is� not� implemented.� Direct� DMA� is�

�disabled.�

�64-bit� Target� and� Master� function� with� a� single� 64� kB� memory.� DMA� registers� are� accessible� from� the� PCI� side�

�and� are� memory-mapped� in� the� second� BAR.� The� FIFO� recovery� logic� is� not� implemented.� BAR� overflow� logic�

�and� hot-swap� features� are� disabled.� Backend� access� to� the� DMA� registers� is� not� implemented.� Direct� DMA� is�

�disabled.�

�64-bit� Target� and� Master� function� with� five� memory� BARs� that� have� variable� sizes� from� 64� kB� to� 1� GB.� The�

�DMA� registers� are� memory-mapped� to� the� sixth� BAR.� All� of� the� memory� BARs� include� the� FIFO� recovery�

�logic.� The� Expansion� ROM� address� registers� are� also� implemented.� BAR� overflow� logic� and� hot-swap� features�

�are� enabled.� Backend� access� to� the� DMA� registers� is� also� implemented.� Direct� DMA� is� enabled.�

�v4.0�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

COREU1LL-AR

IP MODULE COREU1LL

COREU1PHY-AR

IP MODULE COREU1PHY

CORR-8BIT-XM-UT2

SITE LICENSE IP CORRELATOR XP

CP2-GSA-L

CONN SHIELD LOWER TYPE A 22

CP2-HSA110-1

CONN SHROUD CPCI 2MM TYPE A 22

CP2-HSC055-4

CONN SHROUD CPCI 2MM TYPE C 11

CP2-K3567-SR-F

COMPACT PCI - MISC

CP2105EK

KIT EVAL FOR CP2105

相关代理商/技术参数

COREPCIF-RMFL

功能描述:IP MODULE 制造商:microsemi corporation 系列:- 零件状态:在售 类型:许可证 应用:- 版本:- 许可长度:- 许可 - 用户明细:- 操作系统:- 配套使用产品/相关产品:Microsemi 器件 媒体分发类型:- 标准包装:1

COREPCIF-UR

功能描述:HW/SW/OTHER 制造商:microsemi corporation 系列:* 零件状态:在售 标准包装:1

COREPCI-SN

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CorePCI v5.41

COREPCI-SR

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CorePCI v5.41

COREPCI-UR

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CorePCI v5.41

COREPCI-XX

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CorePCI v5.41

COREPRO LEDBULB 10.5-60W B

制造商:Philips Lumileds 功能描述:

COREPRO LEDBULB 10.5-60W E

制造商:Philips Lumileds 功能描述: